# 홀로그램 영상서비스를 위한 홀로그램 직접획득 및 하드웨어 CGH 생성 기술

□ 흥기훈, 권원옥, 최기홍 / 한국전자통신연구원

#### 요 약

스타워즈의 레아 공주 홀로그램을 통해 홀로그램이 대중적으로 소개된 이후 40여 년이 지났지만 영화에서 묘사된 장면은 아직실현되지 못하고 있다. 본 기술기고에서는 이러한 홀로그램 영상서비스를 실현하기 위한 여러 가지 요소기술들 중 실제 환경 또는 사람의 3차원 정보를 직접획득한 컨텐츠 확보를 위한 자가간섭 홀로그래피 기술을 이용한 자연광 기반 홀로그램 직접획득 기술과 소형, 저전력화가 가능한 실시간 홀로그램 하드웨어 생성 기술인 FPGA 기반 홀로그래픽 프로세서를 이용한 실시간 CGH하드웨어 생성 기술의 연구 동향에 대해 소개한다.

## I. 서 론

디지털 홀로그래피 기술은 1977년 개봉한 영화 '스타워 즈4-새로운 희망'에서 등장한 레아 공주의 홀로그램 등장 장면을 통해 대중들에게 널리 알려졌다. 이 장면을 통해 디지털 홀로그래피 기술은 3차원 정보를 있는 그대로 기록하고 이를 이용하여 실재와 동일한 영상을 재현하는 것으로, 기존의 회절 및 간섭 이론을 이해해야 했던 복잡하고 어렵다고 여겨지던 홀로그래피라는 기술을 시각적으로 이해하기 쉽게 대중에게 소개하였다. 레아 공주 홀로그

램은 현실적인 컬러 3차원 영상을 제공하며, 시청 환경에 제한이 없어 다수의 시청자가 동시에 이를 즐길 수 있는 모습으로 음성과 영상을 결합한 멀티미디어 통신 기능과 원격 지역 간의 실시간 영상서비스 기능을 제공하여 효율적인 커뮤니케이션이 가능한 것으로 묘사되었다.

그러나 현재의 디지털 홀로그래피 기술은 40여 년 전에 이 공상과학 영화에서 묘사한 장면과 달리 여러 가지 제약이 존재한다. 컴퓨터 그래픽스로부터의 홀로그램인 CGH(computer generated hologram)가 아닌 실제 환경 또는 사람의 3차워 정보를 직접획득한 홀로그램 컨텐츠가

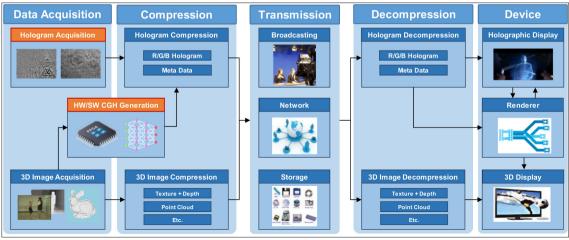

<그림 1> 홀로그램 영상서비스 시나리오 예시

부재하며, 재현된 홀로그램 영상은 여전히 시야각 등 시청 환경과 화질 등의 영상 품질이 제한되며 홀로그램을 실시 간으로 획득 또는 생성하여 재생하는 홀로그래픽 미디어 는 아직까지 불가능한 것이 현실이다.

대중들의 홀로그램 영상에 대한 호기심과 이에 따른 요구로 홀로그래픽 디스플레이에 대한 연구 개발은 꾸준히 진행되고 있다. 한국전자통신연구원에서는 수평 360도 전방향에서 시청 가능한 5인치 영상 크기, 30fps의 컬러홀로그램을 재생할 수 있는 테이블탑형 홀로그래픽 디스플레이를 개발하여 대중이 자연스럽게 홀로그램 영상을 시청할 수 있는 기술을 소개하였다. 최근에는 Microsoft, Nvidia, Meta 등의 글로벌 기업에서 가상/증강현실 응용에서 디지털 홀로그래피 기술을 적극적으로 적용하고 있다. 이러한 가상/증강현실 응용 홀로그래픽 디스플레이는 인공지능 기술을 결합하여 홀로그램의 화질을 향상시키고, 근안디스플레이 기기 수준의 소형화를 추구하여 홀로그램 기술의 보다 넓은 적용 가능성을 보이고 있다.

이처럼 홀로그래픽 디스플레이의 발전을 위한 연구는 현재 진행형이지만 홀로그램을 이용하여 미디어체인을 구현하기 위한 홀로그램 영상서비스에 대한 고민은 이제 시작 단계이다. 현재까지 개발된 디지털 홀로그램 기술 들은 홀로그램 영상서비스의 가능성을 열어놓았지만, 이 를 실현하기 위해서는 몇 가지 기술적인 문제들을 해결 해야 한다.

한국전자통신연구원에서는 스타워즈 영화에서 묘사한 것과 같은 홀로그램 영상서비스를 구현하기 위해 〈그림 1〉 과 같은 홀로그램 영상서비스 시나리오를 제시하고 홀로 그램 영상서비스를 위한 다양한 기술적 고민과 연구를 진 행하고 있다. 이를 위해 자연광 기반 홀로그램 직접 획득 기술을 통해 실제 환경이나 대상물체에 대한 홀로그램 컨 텐츠를 확보하고. HW/SW 홀로그램 생성 기술을 통해 기 존의 3차원 영상정보(RGBD, Point cloud, light field 등) 로부터 홀로그램을 실시간으로 생성하는 연구와 하드웨 어 응용을 위한 소형/고성능/저전력화가 가능한 하드웨 어 CGH 생성기 개발을 진행하고 있다. 또한 홀로그램 압 축 기술을 통해 대용량 복소 홀로그램의 데이터량을 축소 하고, 홀로그램 렌더링 기술을 통해 홀로그램의 생성과 재 현 환경 사이 의존성을 해결하기 위한 변환 기술, CGH 와 직접획득 홀로그램을 합성 저작하는 연구도 함께 진 행 중이다.

본 기술기고문에서는 이러한 홀로그램 영상서비스 시 나리오 구현을 위해 요구되는 다양한 요소기술들 중 자가 간섭 홀로그래피 기술을 이용한 자연광 기반 홀로그램 직 접획득 기술과 FPGA(field-programmable gate array) 기반 홀로그래픽 프로세서를 이용한 실시간 CGH 하드웨 어 생성 기술에 대한 연구 동향에 대해 논의한다

## II. 자가간섭 홀로그래피 기술을 이용한 자연광 기반 홀로그램 직접획득 기술

기존의 고전적인 홀로그램 직접획득 기술은 레이저 등의 가간섭성이 높은 광원이 필수로 요구되어 안전 등의문제로 제한된 실험실 환경에서만 가능한 기술로 여겨졌다. 또한 직접획득한 홀로그램 영상에는 빛의 간섭 원리에 따라 불가피하게 발생하는 광원(bias)과 쌍영상(twinimage) 노이즈가 포함돼 있으며, 이들 노이즈가 제거된복소 홀로그램을 얻기 위해서는 위상천이 기법을 사용해야 한다. 이 기법을 적용하려면 시간적 차이를 가지고 위상의 차이를 가지며 획득된 여러 장의 간섭무늬 이미지를획득해야 한다. 이러한 과정 때문에 실시간으로 홀로그램을 직접 획득하는데 어려움이 있다.

이러한 문제를 해결하기 위해 짧은 가간섭거리를 가 지는 다양한 조명 조건에서도 홀로그램을 직접획득할 수 있는 기하위상 기반 자가간섭 홀로그래피(geometric phase-self interference incoherent digital holography, GP-SIDH) 등 다양한 방식의 자연광 기반 홀로그램 직접 획득 기술이 제안되었다[1] 이후 실시간성을 더하기 위해 픽셀마다 서로 다른 각도를 가지는 선형편광판들이 위치 하는 편광이미지 센서를 자가간섭 홀로그래피에 적용하 는 기술들이 소개되었다[2]. 하지만 현재 시장에서 판매되 고 있는 편광이미지 센서가 매우 제한적인 이유로 인해 직 접획득할 수 있는 해상도에 한계가 발생한다. 또한, 편광 이미지 센서를 적용한 자가간섭 홀로그래피 기술들은 네 개의 편광 하위 픽셀 값을 결합하는 위상천이 기법을 활용 하는 것으로, 이 과정을 통해 얻은 복소 홀로그램의 가로 와 세로 해상도가 절반으로 줄어들게 되어 유효 픽셀 크기 와 입력 빛의 파장에 의해 정의된 최대 주파수 근처에서 획득 가능한 고주파 정보 또한 감소하는 한계를 가진다.

자가간섭 홀로그래피로 획득한 영상은 각각의 물체점에 해당하는 간섭성을 가지지 않는 단위 홀로그램 패턴의 누적합으로 이루어진 홀로그램으로 생각할 수 있다. 이때 단위 홀로그램 패턴이 가지는 노이즈의 정도가 적더라도 최종적으로 촬영된 홀로그램에서는 이들이 누적되어 실제 대상 물체가 가지는 3차원 영상 정보 신호 대비 노이즈의 정도가 매우 높아지는 한계를 가진다. 또한 자가간섭 홀로그래피에 사용되는 광학소자의 불완전성 및 수차와 편광소자 적용에 따른 저조도 환경에서의 직접획득에 따라 추가적인 영상 잡음 문제가 발생한다.

최근 삼성전자가 경희대학교와의 공동연구를 통해 자 가간섭 홀로그래피 기술에 딥러닝 기반 잡음 저감 기법을 적용하여 이러한 신호대잡음비가 낮은 한계를 극복하고 자 하는 연구 결과를 보고하였다[3] 신경망 훈련을 위한 데이터셋 확보를 위해 다양한 깊이에 위치한 모니터 상의 2D 영상을 자가간섭 홀로그래피를 이용하여 직접획득하 는 방식을 사용하였으며, 직접획득한 낮은 신호대잡음비 를 가지는 홀로그램의 가운데 600 x 600 픽셀 영역을 관심 영역으로 지정하여 준비한 데이터셋을 이용하여 지도 학 습 방식의 신경망에 훈련시키는 방식을 사용하였다. 결과 적으로 최대 21fps의 속도로 PSNR 기준 원본 10dB 수준 의 영상 화질을 평균적으로 19.8dB를 가지도록 향상시키 는 결과를 보였다. 이 잡음 저감 연구는 딥러닝 기반의 신 경망을 최초로 자가간섭 홀로그래피에 적용한 기술로 기 존의 디지털 홀로그래피에서의 잡음 저감 기법이 수치적 으로 특정 깊이에서 재구성된 2D 평면 영상에 제한되는 것과 달리 잡음이 저감된 복소 홀로그램을 출력으로 한다 는 장점을 가진다.

한국전자통신연구원에서는 GP-SIDH를 기반으로 일반 이미지센서를 실시간 자가간섭 홀로그래피에 적용하여 홀로그램을 실시간으로 획득하여 기존 편광 이미지센서의 픽셀 수로 해상도가 제한되는 문제를 해결하는 연구 [4]와 광학계의 편광 수차 및 자가간섭 홀로그래피의 낮은 신호대잡음비를 개선하기 위한 딥러닝 기반 직접획득 홀로그램의 화질 개선 연구[5]를 진행하고 있다.

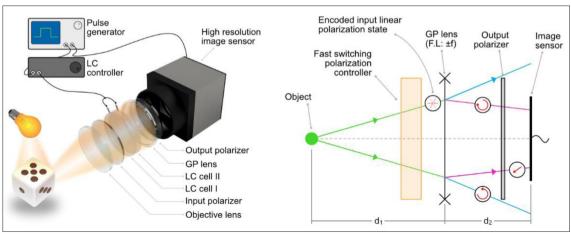

<그림 2> 고속 편광 스위칭 기반 자연광 홀로그램 직접획득 시스템 개념도[4]

편광이미지 센서에 의존적인 기존 실시간 자가간섭 홀로그래피 기술의 문제를 해결하기 위해 한국전자통신연 구원이 경북대학교와 공동연구를 통해 제안한 일반 고해 상도 이미지센서를 사용할 수 있는 고속 편광 스위칭 기반 자연광 홀로그램 직접획득 시스템의 개념도는 〈그림 2〉와 같다. 고속 편광 스위칭 장치는 두 개의 이중 액정 셀과

기하학적 위상 렌즈 및 편광기로 구성되며, 99Hz의 속도로 세 단계의 기하위상 변이를 구현할 수 있다. 이를 광원과 쌍영상 제거를 위한 위상천이 기법에 적용하여 일반 이미지센서의 해상도를 모두 사용하여 33fps의 속도로 20메가 픽셀 이상의 해상도를 가지는 복소 홀로그램 비디오를 획득할 수 있는 것을 특징으로 한다.

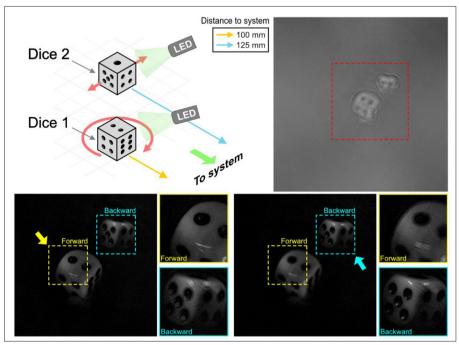

<그림 3> 고속 편광 스위칭 기반 자연광 홀로그램 직접획득 결과[4]

<그림 4> U-Net 기반 딥러닝 복소 홀로그램 노이즈 개선 네트워크 적용 결과[5]

제안한 고속 편광 스위칭 기반 자연광 홀로그램 직접 획득 기술을 이용하여 얻은 홀로그램과 수치복원 결과는 〈그림 3〉과 같으며, 결과에서 볼 수 있듯 이 기술은 기존 편광 이미지센서 사용 시 복소 홀로그램 데이터의 가로 및 세로 픽셀 수가 절반으로 감소하는 문제를 해결할 수 있으며 홀로그램의 높은 주파수 영역을 충실히 기록하는 동시에 실시간으로 자연광 조건에서 홀로그램을 직접획득할 수 있다는 장점을 가진다.

현재 한국전자통신연구원에서는 높은 해상도를 가지는 직접획득 홀로그램에 대해 개선된 화질의 홀로그램을 출력할 수 있는 복소 U-Net 구조의 잡음 저감 네트워크를 개발하고 있다. 기존 연구에서 홀로그램 전체 영역 중 신호대잡음비가 높은 관심영역을 대상으로만 화질 개선된 홀로그램을 추론하는 것과 달리, 한국전자통신연구원에서 개발 중인 네트워크는 입력되는 신호대잡음비가 낮은 직접획득 복소 홀로그램이 가지는 해상도와 동일한 크기를 가지는 화질 개선 컬러 복소 홀로그램 데이터가 출력되는 장점을 가진다.

훈련 데이터로는 총 7개의 깊이에서 GP-SIDH 방식으로 직접획득한 500장의 홀로그램을 사용했으며, 제안한 U-Net 기반 딥러닝 복소 홀로그램 노이즈 개선 네트워크를 통한 결과는 〈그림 4〉와 같다. 결과 그림에는 왼쪽부터 원본과 추론된 노이즈 개선 홀로그램의 위상각 영상, 원본과 노이즈 개선 홀로그램의 수치복원 영상을 보여준다. 제안한 노이즈 개선 네트워크를 적용한 1,024 x 1,024 해상도를 가지는 직접획득 홀로그램 입력영상에 대한 수

치복원 결과는 기존 PSNR 10dB 수준에서 20dB 수준으로 화질이 개선되었으며 기존 방식과는 다르게 영상정보가 부족한 주변부 또한 복원되며 노이즈가 저감되는 결과를 얻었다.

## III. FPGA 기반 홀로그래픽 프로세서를 이용한 실시간 CGH 하드웨어 생성 기술

최근 인공지능 기술을 CGH 기술에 접목하여 CGH 생 성 속도와 화질을 혁신적으로 개선한 연구들이 다수 발표 되었다[6.7] 이러한 딥러닝 기반 CGH 기술들은 기존 디 지털 홀로그래피의 난제라 여겨지고 있던 방대한 계산량 과 스페클 등에 의한 화질 문제에 대한 해결책으로 부상하 고 있으나, 학습과 추론에 높은 사양의 그래픽 처리 장치 가 요구된다. 다른 한편으로는 자동차용 헤드업디스플레 이(head up display, HUD) 등의 응용에 홀로그래피 기 술을 적용하여 증강(augmented reality, AR)정보를 추가 로 제공하고자 하는 산업체의 시도도 활발하게 진행 중이 다[8,9]. 자동차용 AR-HUD에서는 제한된 하드웨어 볼륨 에서 큰 FoV(field of view) 및 여러 깊이의 VID(virtual image distance)를 제공해야 하는 기술적 어려움을 가 지고 있어 이를 해결할 수 있는 홀로그래피 광학소자와 CGH 적용이 적극적으로 고려되고 있다. 특히 CGH를 AR-HUD에 적용하면 기존의 광학 구조를 축소할 수 있 어 패키징 크기를 줄일 수 있으며 홀로그램 이미지를 생성 하여 모든 초점 면에서 이미징이 가능해진다는 이점이 있다. 이러한 자동차용 AR-HUD에 디지털 홀로그래피 기술을 적용하기 위해서는 광학시스템 외에도 CGH 생성이 소형, 저전력 하드웨어 모듈로 실시간 처리가 가능해야 하지만 이는 딥러닝 기반 CGH 기술로는 구현이 어렵다. 이러한 최근 산업체의 요구로 인해 실시간 CGH 하드웨어 생성기술에 대한 관심이 다시금 증가하고 있다.

일본 치바대에서는 1990년대부터 포인트클라우드로 구성된 3차원 영상정보부터 홀로그램을 생성하는 HORN으로 이름 붙여진 FPGA 기반의 하드웨어 시스템을 연구, 개발해 오고 있으며, 최근 연구에서는 한 개의 FPGA 기반 HORN-9 시스템으로 65,000개의 물체점으로 표현된 포인트클라우드 3차원 이미지를 1,920 x 1,080의 해상도와 33fps 속도로, 4개의 HORN-9 시스템을 클러스터로 구축하여 400,000개 물체점의 포인트클라우드 3차원 이미지를 동일 해상도 조건에서 125fps의 속도로 홀로그램으로 생성하는 결과를 보고하였다[10]

삼성전자에서는 최근 슬림패널 홀로그래픽 비디오 디스플레이 연구 결과를 발표하였다[11]. 이 연구에서 슬림 디스플레이 형태의 하드웨어 크기 내에서 홀로그래픽 디

스플레이를 구현하기 위해 광학계를 경박단소화하고 실시간 홀로그래픽 비디오 프로세서를 FPGA로 구현한 결과를 보고하였다. 밝기와 깊이 정보를 가지는 RGBD 영상을 입력영상으로 받아 8개의 깊이 layer를 가지는 홀로그램을 3,840×2,160의 해상도, 30fps의 속도로 생성할수 있도록 FPGA를 구현하였다. CGH 생성을 위해 2번의 FFT 연산이 요구되는 Cascaded general Fresnel transform 전파방식을 사용하였으며 이를 32개의 1-D IFFT 프로세서로 구현하고 복소 홀로그램 테이터를 32bit로 처리, pupil space division method를 적용 주파수 공간에서의 고주파수 성분을 메모리에 읽고 쓰지 않는 방법등을 적용하여 메모리 사용량을 최소화하였다.

앞장에서 설명한 자가간섭 홀로그래피 기술을 이용한 자연광 기반 홀로그램 직접획득 기술을 통해 얻은 홀로그램의 수치복원을 실시간으로 수행하기 위해 FPGA 하드웨어를 적용하는 연구 또한 최근 일본 치바대에서 발표하였다[12]. 홀로그램을 단일 깊이로 수치복원하는 것과 달리 조밀한 depth sliced 영상들로 3차원 볼륨을 복원하기위해서는 계산량이 폭발적으로 증가하는 것을 대비한 연구로 보이며, 아직까지는 직접획득한 홀로그램이 아닌 일

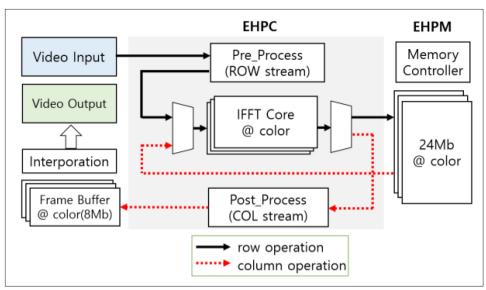

<그림 5> 단일 깊이 홀로그램 코어 아키텍쳐 구조[13]

반적인 CGH를 입력영상으로 하였으나 256 x 256 해상도의 CGH를 10-core CPU로 계산한 것 대비 9배 정도 속도를 개선한 결과를 보고하여 실제 자연광 조건에서 직접획득한 홀로그램 데이터로의 적용 가능성을 보였다

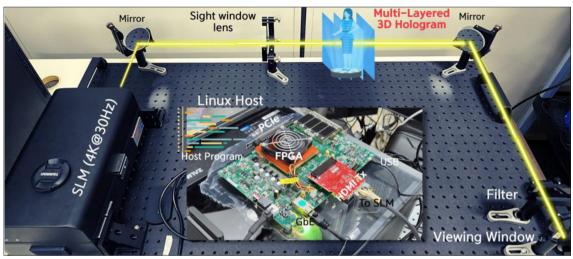

한국전자통신연구원에서도 밝기와 깊이 정보를 가지는 3차원 정보영상을 입력영상으로 하여 실시간 CGH 하드웨어 생성 기술인 실시간 홀로그래픽 비디오 프로세서 개발을 진행 중이다. 2023년 단일 FFT를 이용하여 홀로그램을 생성할 수 있는 modified inverse Fresnel transform알고리즘을 적용한 확장이 용이한 FPGA 기반 단일 깊이홀로그램 코어 아키텍쳐를 제안하였다[13]

제안한 단일 깊이 코어 아키텍쳐 구조는 〈그림 5〉와 같다. 고정 소수점 모델을 사용하여 단일 깊이에 해당하는 홀로그래피를 계산하는 코어 아키텍쳐를 설계하고 FPGA로 구현하였으며, 단색 밝기와 깊이 입력영상에서의 1k × 1k 해상도 영역을 코어 아키텍쳐 FPGA에서 한 번의 FFT로 처리하여 22ms 이내에 홀로그램으로 변환하고 4K 컬러 공간광변조기에서 30fps의 속도로 실시간 재현할 수

있으며, 가용한 FPGA 하드웨어 대비 상대적으로 적은 로 직을 사용하여 확장이 용이하다는 것을 특징으로 가진다

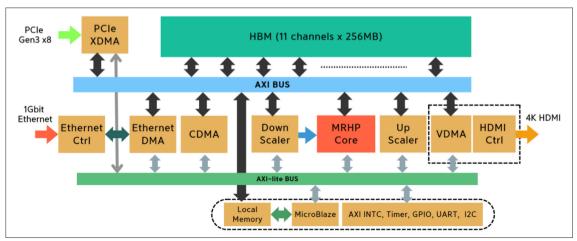

현재 한국전자통신연구원에서는 위 단일 깊이 홀로그래피 코어 아키텍쳐를 확장하여 RGB 컬러 채널의 밝기와 깊이 입력영상으로부터 15fps의 속도로 2K x 2K 해상도의 8개 깊이 정보를 가지는 홀로그램으로 변환할 수 있는 FPGA 기반 다중 깊이 실시간 홀로그래픽 비디오 프로세서를 개발하였다. 빠른 CGH 처리를 위해 DDR4보다 빠른 HBM 메모리를 사용하여 FFT 결과를 저장하고 입력영상의 저작이 용이하고 확장성이 높은 PCIe 또는 UDP의입력영상 인터페이스를 적용하였으며, 이를 통해 밝기와 깊이 영상을 입력으로 받아 FPGA 자원 제한과 인간의 깊이 분해능을 고려한 8개의 깊이면에 해당하는 깊이 정보만 홀로그램으로 변환하는 특징을 가진다.

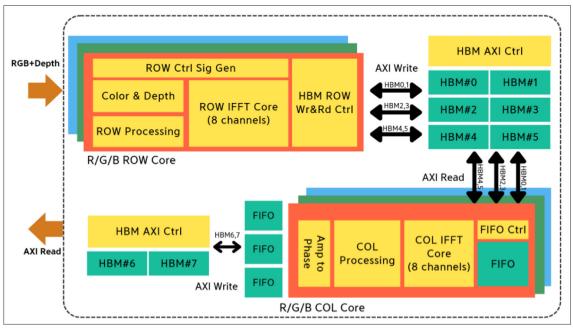

개발한 다중 깊이 실시간 홀로그래픽 비디오 프로세서에서 홀로그램 계산을 수행하는 RGB 다중 깊이 코어 아키텍쳐의 구조는 〈그림 6〉과 같다. 입력영상의 행, 열방향 1D IFFT를 각각 수행하는 ROW, COL core와 HBM

<그림 6> RGB 다중 깊이 홀로그램 코어 아키텍쳐 구조

<그림 7> 다중 깊이 실시간 홀로그래픽 비디오 프로세서의 전체 아키텍쳐 구조

으로 구성된다. ROW, COL core는 3채널의 RGB 영상마다 동일한 core를 겹쳐 사용하며, 8개의 깊이에 대한 정보를 처리하므로 총 48개의 FFT 코어가 사용된다. HBM은 ROW IFFT 결과를 저장하는 부분(HBM#0-#5)과 결과 홀로그램의 위상영상 출력을 저장하는 부분(HBM#6, #7)으로 구분된다. 버스트 방식, 무작위 방식의 읽기 및 쓰기 방식을 가지는 ROW core와 COL core의 HBM 메모리로의접근 속도 차이를 보상하기 위해 각 컬러 채널에 대해 이중 버퍼링 메모리 구조를 구현하였다.

RGB 다중 깊이 홀로그램 코어 아키텍쳐를 포함하는 FPGA 기반 다중 깊이 실시간 홀로그래픽 비디오 프로 세서의 전체 아키텍쳐 구조는 〈그림 7〉과 같다. 기존 RGBD 입력영상에 대한 제한이 있는 HDMI가 아닌 PCIe, Ethernet을 이용한 RGBD 패킷 입력 인터페이스를 가지며 파장의존성을 가지는 홀로그램 생성 특성을 고려하여 RGB 입력의 크기를 선보상하는 Down-scaler와 주변부로지들을 포함하는 것을 특징으로 하며,〈그림 8〉과 같이다중 깊이 실시간 홀로그래픽 비디오 프로세서를 적용한

<그림 8> 다중 깊이 실시간 홀로그래픽 프로세서 적용 홀로그래픽 디스플레이 테스트베드

위상변조 LCoS를 포함하는 시야창 방식의 홀로그래픽 디 스플레이 테스트베드를 구현하였다

### IV. 결 론

홀로그램 영상서비스 구현을 위한 다양한 기술들에 대해 논의하였으며 요구되는 다양한 요소기술들 중 자가간 섭 홀로그래피 기술을 이용한 자연광 기반 홀로그램 직접획득 기술과 FPGA 기반 홀로그래픽 프로세서를 이용한 실시간 CGH 하드웨어 생성 기술의 연구 동향에 대해 살펴봤다. 현재의 연구 동향을 바탕으로, 이 두 분야에서의

기술적 발전은 향후 홀로그래픽 미디어 체인 구현과 디지털 홀로그램 기술의 상업적 응용 및 대중화를 위해 중요한역할을 할 것으로 기대된다. 자연광 기반의 홀로그램 직접획득 기술은 더 높은 해상도와 낮은 노이즈 수준을 달성하기 위해 지속적인 연구가 필요하며, FPGA 기반 실시간 CGH 생성 기술은 더 빠른 처리 속도와 하드웨어 응용을 위한 확장성 개선을 위한 연구가 계속될 것으로 예상된다. 이러한 디지털 홀로그래피 요소기술들의 고도화가현재 추이를 가지면서 향후 이들 간의 융합과 상호작용이이루어진다면 홀로그램 영상서비스라는 새로운 가능성이열릴 것으로 기대한다

\*\* This work was supported by Institute of Information & communications Technology Planning & Evaluation (IITP) grant funded by the Korea government (MSIT) (No. 2019-0-00001, Development of Holo-TV Core Technologies for Hologram Media Services)

#### 참고문헌

- [1] Y. Kim, K.-H. Choi, C. In, K. Hong, and S.-W. Min, "Recent Research on Self-interference Incoherent Digital Holography," Curr. Opt. Photon 8. 1-15 (2024)

- [2] K, Hong and K, Choi, "Single-shot phase-shifting on Michelson interferometry for incoherent digital holography," ETRI J. (2024),

- [3] H. Yu, Y. Kim, D. Yang, W. Seo, Y. Kim, J.-Y. Hong, H. Song, G. Sung, Y. Sung, S.-W. Min, et al., "Deep learning-based incoherent holographic camera enabling acquisition of real-world holograms for holographic streaming system," Nat, Commun. 14, 3534 (2023).

- [4] K. Choi, J.-W. Lee, J. Shin, K. Hong, J. Park, and H.-R. Kim, "Real-time noise-free inline self-interference incoherent digital holography with temporal geometric phase multiplexing," Photon, Res. 11, 906-916 (2023).

- [5] K, Choi, J, Moon, K, Hong, "Complex hologram quality enhancement of incoherent digital holographic camera," in DHIP 2023, 8-2 (2023),

- [6] L. Shi, B. Li, C. Kim, P. Kellnhofer, and W. Matusik, "Towards real-time photorealistic 3D holography with deep neural networks," Nature 591, 234-239 (2021).

- [7] S. Choi, M. Gopakumar, B. Chao, G.-Y. Lee, J. Kim, and G. Wetzstein, "Neural Holographic Near-eye Displays for Virtual Reality," in ACM SIGGRAPH 2023 Emerging Technologies, pp. 1-2 (2023).

- [8] https://wayray.com/

- [9] https://envisics.com/

- [10] Y. Yamamoto, T. Shimobaba, and T. Ito, "HORN-9: Special-purpose computer for electroholography with the Hilbert transform," Opt. Express 30, 38115-38127 (2022).

- [11] J. An, K. Won, Y. Kim, J.-Y. Hong, H. Kim, Y. Kim, H. Song, C. Choi, Y. Kim, J. Seo, et al., "Slim-panel holographic video display," Nat. Commun, 11, 5568 (2020),

- [12] T. Hara, T. Kakue, T. Shimobaba, and T. Ito, "Color Diffraction Computer for Incoherent Digital Holography," IEEE Access (2024).

- [13] W. Kwon, S. Cheon, and J. Park, "76-2: Scalable Real-time Holography Processor Architecture," in SID Symposium Digest of Technical Papers, vol. 54, no. 1, pp. 1076-1079 (2023).

## 저 자 소 개

#### 홍기훈

- 2008년 : 연세대학교 전기전자공학부 학사 - 2014년 : 서울대학교 전기컴퓨터공학부 박사

- 2015년 ~ 현재: 한국전자통신연구원 선임연구원, 디지털홀로그래피연구실 실장

- 주관심분야 : 디지털 홀로그래피, 입체영상 디스플레이

#### 권 원 옥

- 1996년 : 경북대학교 전자공학과 학사 - 2001년 : 경북대학교 전자공학과 석사 - 2011년 : 경북대학교 전자공학과 박사

- 2002년 ~ 현재 : 한국전자통신연구원 책임연구원

- 주관심분야: FPGA, SoC 설계, 컴퓨터 하드웨어 구조 설계, 실시간 홀로그래피 프로세서

#### 최기홍

- 2013년 : 경희대학교 정보디스플레이학과 학사 - 2015년 : 경희대학교 정보디스플레이대학원 석사 - 2019년 : 경희대학교 정보디스플레이대학원 박사 - 2019년 ~ 현재 : 한국전자통신연구원 선임연구원

- 주관심분야: 디지털 홀로그래피, 홀로그램 획득 시스템, 입체영상 디스플레이